# Design and Fabrication of Multi-finger Field Plate for Enhancement of AlGaN/GaN HEMT Breakdown Voltage

Amit, D.S. Rawal<sup>\*</sup>, Sunil Sharma, Sonalee Kapoor, Robert Liashram, Rupesh K. Chaubey, Seema Vinayak, and Rajesh K. Sharma

> DRDO-Solid State Physics Laboratory, Delhi - 110 054, India \*E-mail: ds\_rawal@sspl.drdo.in

#### ABSTRACT

The design and fabrication of gate/source connected multi-finger field plate structures using TCAD ATLAS simulation software is presented. The designed field plate structures are fabricated on indigenous AlGaN/GaN HEMT devices. AlGaN/GaN HEMT devices with field plate structures exhibit about three times improvement in breakdown voltage of device and are in close agreement with the simulation results. Integration of field plates in device have resulted in higher  $V_{DS}$  (drain to source voltage) operation and improvement in output power of AlGaN/GaN HEMT devices. Incorporation of field plates also decrease the reverse leakage current of HEMT devices.

Keywords: GaN; HEMT; Field plate; ATLAS; Breakdown voltage

### 1. INTRODUCTION

Recent advances in gallium nitride (GaN) technology have significantly increased power densities for high electron mobility transistor (HEMT) over previous technologies, such as gallium arsenide (GaAs) and other III/V devices1. This allows not only the production of smaller device with same output power, but also provides much higher device impedance. Higher impedance makes RF matching much easier, eliminating the extra cost and complexity needed for other conventional elements such as based on GaAs. In addition to this, highvoltage property of GaN reduce the need of voltage conversion, leading to higher efficiency operation which in return results in power saving and reduced costs for cooling the system. These characteristics make GaN technology, a highly desirable component for RADAR and military communication systems. Therefore GaN based devices are of strategic importance to defence RF and electronic warfare systems for providing electronic counter measure (ECM) capabilities especially for RF jammer applications.

Field plate structures in AlGaN/GaN HEMT devices are very important for high frequency and high output power operation. Field plates enhance the breakdown voltage of device by decreasing the peak of electric field near gate edge towards drain<sup>2-9</sup>. Field plates also help in reducing the extent of virtual gate formation and thus improve the transient operation of the device<sup>10</sup>. AlGaN/GaN HEMTs with gate Field plate have shown reduced current collapse characteristics<sup>11,12</sup>. Use of field

plates in AlGaN/GaN HEMT improve the low frequency noise of the device but adversely affects the frequency response and power added efficiency performance<sup>13</sup>. Properly designed Field plates enhance the device performance in thermal aspects by reducing the thermal resistance and channel temperature of transistor<sup>14</sup>. The effect of Field plates depends on the quality (stoichiometry) of the passivation film underneath the Field plates structures<sup>15</sup>. In this work we designed and fabricated the source connected and gate connected field plate structures for high power AlGaN/GaN HEMT devices for up to C-band applications. The output power of AlGaN/GaN HEMT devices is proportional to  $V_{DS}$  (source to drain voltage) applied during biasing. The highest  $V_{DS}$  which can be applied safely to the device depends upon the breakdown voltage of the device. So to achieve high output power we need to maximise the breakdown voltage of the device. One of the most popular and important way of enhancing the breakdown voltage of AlGaN/ GaN HEMT device is to reduce peak electric field between gate and drain, using properly designed source and gate connected field plate structures.

### 2. DESIGNING OF FIELD PLATES

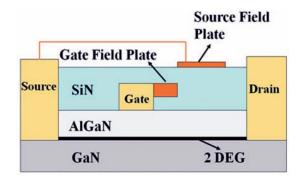

Multi-finger field plates have been designed using TCAD ATLAS software. We have used two field plate structures that is source connected and gate connected field plates. Field plate schematics are as shown in Fig. 1. ATLAS software is calibrated to match our indigenously fabricated HEMT experimental results. Two dimensional electron gas (2DEG) is generated using interface statement and is set equal to the experimentally measured sheet carrier concentration. Contact resistances of

Received : 27 October 2017, Revised : 24 January 2018 Accepted : 25 March 2018, Online published : 16 April 2018

Figure 1. Schematics of gate connected and source connected field plates.

ohmic contacts, Schottky barrier height of gate contact, low field mobility are set equal to the experimentally measured values of these parameters. Low  $V_{DS} = I_D$  (drain current) - $V_{GS}$  (source to gate voltage) characteristics are simulated and matched with measured  $I_D - V_{GS}$  characteristics. The off-state gate and drain leakage currents can significantly affect the breakdown phenomenon in device. So simulated off-state gate and drain leakage currents are matched to experimentally measured leakage currents. Selberherr's Impact Ionisation model is used to simulate breakdown phenomenon.

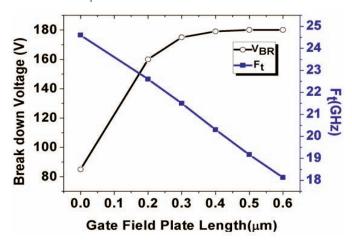

To optimise the gate connected field plate length, breakdown characteristics and  $F_T$  (cut-off frequency) are simulated for different  $L_{GFP}$  (gate field plate length).  $L_{GFP}$  is varied from 0.2 µm in steps of 0.1 µm till the breakdown voltage value saturates. The  $L_{GFP}$  optimisation results are as shown in Fig. 2.

Optimised  $L_{\rm GFP}$  is 0.6 µm and breakdown voltage is more than doubled after using gate connected field plate. Gate connected field plate increases the gate capacitance thereby reducing the  $F_{\rm T}$  of the HEMT device.

Figure 2. Optimisation of gate connected field plate at  $V_{GS}$  = -7V. No source field plate is considered in gate connected field plate optimisation.

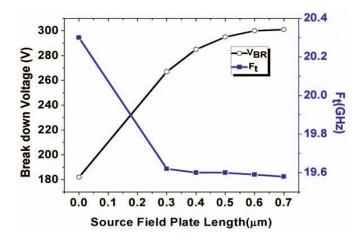

SiN layer of fixed thickness is deposited over the gate connected field plate by plasma enhanced chemical vapour deposition system (PECVD). Source connected field plate is then optimised using 0.6  $\mu$ m gate connected field plate and SiN layer thickness between these two field plates. Results of Source field plate optimisation are as shown in Fig. 3.

Figure 3. Optimisation of source connected field plate at  $V_{GS}$ = -7V. The length of gate field plate is 0.6 µm.

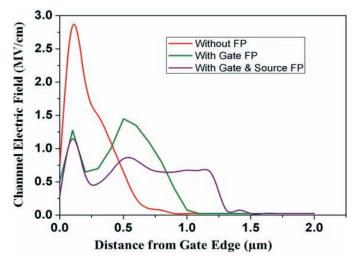

Simulation results show that by using both gate connected and source connected filed plates the breakdown voltage is enhanced by more than three times. Fig. 4 shows the distribution of lateral electric field in HEMT device channel with distance from the gate edge towards drain contact at  $V_{DS} = 85V$ .

Field Plates have decreased the peak value of electric field in channel by dividing it in three peaks. This leads to enhancement in breakdown voltage of the AlGaN/GaN HEMT devices.

Figure 4. Channel electric field distribution with and without field plates.

#### 3. FABRICATION AND MEASUREMENTS

The typical MOCVD grown HEMT structure used for device fabrication is consists of a GaN buffer layer, AlN spacer layer, AlGaN barrier layer and thin GaN cap layer. Hall-effect measurements showed a two-dimensional electron gas (2DEG) density of ~ $1.0x10^{13}$  cm<sup>-2</sup> and an electron mobility of ~1800cm<sup>2</sup>/Vs. The device fabrication starts with source and drain ohmic contacts formation by e-beam evaporation followed by device isolation using BCl<sub>3</sub>/Cl<sub>2</sub> based inductively coupled plasma reactive ion etching (ICP-RIE) for dry etching. This is followed by formation of Ni/Au gate Schotky contacts ~ $0.7\mu$ m gate length. Devices are then passivated by a thin SiN layer using PECVD process.

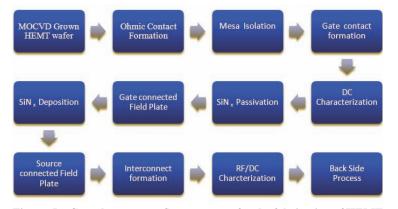

Designed Field Plates are then fabricated on AlGaN/ GaN HEMT by formulating a compatible process flow incorporating steps for gate and source connected field plates as described. Contact Windows are opened in SiN passivation layer by using  $CF_4/O_2$  based dry etching. Bi-layer resist process is used for gate field plate lithography followed by Ti/Au metal deposition in e-beam metal deposition system. Finally Lift-off is done to remove unwanted metal. Similarly Source connected field plates are fabricated after deposition of SiN layer by PECVD process. The complete process flow is as depicted in Fig. 5. DC and pulse IV characteristics, before/after SiN passivation, are measured using Agilent B1500 parametric analyser and GaAscode pulse IV system respectively. FESEM characterisation is used to ensure the proper field plates placement over the gate.

Figure 5. Complete process flow sequence for the fabrication of HEMT with multi-finger field plates.

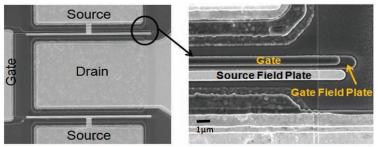

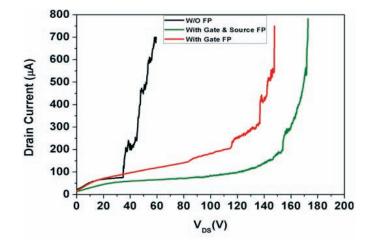

FE-SEM image of fabricated gate connected and source connected field plate is shown in Fig. 6. The fabricated field plates are exactly as per the designed structures. Three different devices including AlGaN/GaN HEMT without field plates, with gate connected field plates and with both Gate and source connected field plates are fabricated on single wafer. Comparison of breakdown characteristics with field plates is as shown in Fig. 7. AlGaN/GaN HEMT devices with both Gate and Source connected field plates exhibit breakdown voltage of about 150 V whereas the breakdown voltage is the voltage measured @ leakage current 1mA/mm). HEMT devices with only Gate connected Field Plate have breakdown voltage

Figure 6. FE-SEM image of fabricated gate and source field plates.

Figure 7. Breakdown characteristics of fabricated AlGaN/GaN HEMT devices at V<sub>GS</sub>=-7V.

of about 130 V. The enhancement in breakdown voltage with Field plates is more than three times. Breakdown characteristics are in trend with prediction of simulation results, although there is a difference in simulated and experimentally measured initial breakdown voltage values without field plates. This may be due to the process issues difficult to include in simulation. The enhancement of breakdown voltage by incorporating field plates, increased the device operating voltage suitability up to 50 V operation. Also with field plates, due to reduction in peak electric field, the availability of active electron taps between gate and drain reduces drastically that results in minimum current collapse and knee walkout.

Hence the incorporation of multi finger field plate is increasing the device breakdown voltage in addition to reduction in current collapse, thus enhancing the total power output of the HEMT device. In other words, field plated device structure enhanced the operating voltage range from 28 V to 50 V without significant reduction in source drain current. The power output increased by ~60 per cent at 50 V in comparison to 28 V of operation for 1mm gate width of HEMT device at 3.0 GHz.

#### 4. CONCLUSIONS

Multi-finger field plates are very much effective in enhancing the breakdown voltage and hence output power of AlGaN/GaN HEMT devices. The designed Gate connected and Source connected Field Plates increased the breakdown voltage by more than three times, making HEMT device suitable for 50 V  $V_{DS}$  operation. The designed field plates are

successfully implemented on AlGaN/GaN HEMTs through a well formulated process sequence. The simulated results of breakdown voltage are in very good agreement with the experimental results of GaN HEMT fabricated with field plates and therefore validated the multi-finger field plate design and fabrication process of Field Plates structures. Also the RF power output with field plate increased by ~60 per cent at 50 V for 1mm gate width of HEMT device at 3.0 GHz.

# REFERENCES

Karmalkar, Shreepad; Sathaiya, D. Mahaveer & Shur, M.S. Mechanism of the reverse gate leakage in AlGaN/ GaN high electron mobility transistors. *Appl. Phys. Lett.*, 2003, 82, 3976.

doi:10.1109/TED.2005.859568

- Karmalkar, Shreepad; Shur, Michael S.; Simin, Grigory & Khan, M. Asif. Field-plate engineering for HFETs. *IEEE Trans. Electron Devices*, 2005, **52**(12), 2534–2540. doi: 10.1109/LED.2003.822667

- Wu, Y.-F.; Wu, Y.-F.; Saxler, A.; Moore, M.; Smith, R. P.; Sheppard, S.; Chavarkar, P.M.; Wisleder, T.; Mishra, U.K. & Parikh, P. 30-W/mm GaN HEMTs by field plate optimization. *IEEE Electron Device Lett.*, 2004, 25(3), 117–119.

- Ando, Y.; Okamoto, Y.; Miyamoto, H.; Nakayama, T.; Inoue, T. & Kuzuhara, M. 10-W/mm AlGaN-GaN HFET with a field modulating plate. *IEEE Electron Device Lett.*, 2003, 24(5), 289–291. doi:10.1109/LED.2003.812532

- Wakejima, A.; Ota, K.; Matsunaga, K. & Kuzuhara, M. A GaAs-based field-modulating plate HFET with improved WCDMA peak-output-power characteristics. *IEEE Trans. Electron Devices*, 2003, **50**(9), 1983–1987. doi:10.1109/TED.2003.815577

- Okamoto, Y.; Ando, Y.; Miyamoto, H.; Nakayama, T.; Inoue, T. & Kuzuhara, M. An 80 W AlGaN/GaN heterojunction FET with a field-modulating plate. *IEEE MTT-S Int. Symp. Dig.*, 2003, 1, 225–228. doi: 10.1109/MWSYM.2003.1210921

- Li, J.; Cai, S.J.; Pan, G.Z.; Chen, Y. Z.; Wen, C.P. & Wang, K.L. High breakdown voltage GaN HFET with field plate. *Electron. Lett.*, 2001, **37**, 196–197. doi:10.1049/el:20010091

- Zhang, N.-Q.; Keller, S.; Parish, G.; Heikman, S.; DenBaars, S.P. & Mishra, U.K. High breakdown GaN HEMT with overlapping gate structure. *IEEE Electron Device Lett.*, 2000, 21(9), 421–423. doi:10.1109/55.863096

- Asano, K.; Miyoshi, Y.; Ishikura, K.; Nashimoto, Y.; Kuzuhara, M. & Mizuta, M. Novel high power AlGaAs/ GaAs HFET with a field modulating plate operated at 35 V drain voltage. *IEDM Tech. Dig.*, 1998, 59-62. doi:10.1109/IEDM.1998.746246

- Brannick, Alan; Zakhleniuk, Nick; Ridley, Brian K. & Eastman, Lester F. Influence of field plate on the transient operation of the AlGaN/GaN HEMT. *IEEE Electron Device Lett.*, 2009, **30**(5), 436–438. doi:10.1109/LED.2009.2016680

- Hasan, Md. Tanvir; Asano, Takashi; Tokuda, Hirokuni & Kuzuhara, Masaaki Current collapse suppression by gate field-plate in AlGaN/GaN HEMTs. *IEEE Electron Device Lett.*, 2013, **34**(11), 1379–1381. doi:10.1109/LED.2013.2280712

- 12. Huang, Huolin; Liang, Yung C.; Samudra, Ganesh S.; Chang, Ting-Fu & Huang, Chih-Fang Effects of gate field plates on the surface state related current collapse in AlGaN/GaN HEMTs. *IEEE Trans. Power Electronics*,

2014, **29**(5), 2164–2173.

- doi:10.1109/TPEL.2013.228864413. Chiu, Hsien-Chin; Yang, Chih-Wei; Wang, Hsiang-Chun;

- 13. Chiu, Fislei-Chin, Fang, Chin-wei, Wang, Fislang-Chun, Huang, Fan-Hsiu; Kao, Hsuan-Ling & Chien, Feng-Tso. Characteristics of AlGaN/GaN HEMTs with various fieldplate and gate-to-drain extensions. *IEEE Electron Device Lett.*, 2013, **60**(11), 3877–3881. doi:10.1109/TED.2013.2281911

- Šodan, Vice; Oprins, Herman; Stoffels, Steve & De Wolf, Ingrid. Influence of Field-plate configuration on power dissipation and temperature profiles in AlGaN/GaN on silicon HEMTs. *IEEE Electron Device Lett.*, 2015, 62(8), 2416–2422.

doi:10.1109/TED.2015.2439055

Waller, William M.; Gajda, Mark; Pandey, S. & Kuball, Martin. Impact of silicon nitride stoichiometry on the effectiveness of AlGaN/GaN HEMT field plates. *IEEE Trans. Electron Dev.*, 2017, 64(3), 1197–1202. doi:10.1109/TED.2017.2654800

## ACKNOWLEDGEMENTS

The authors would like to thank entire GaN team at SSPL, Delhi and GAETEC Hyderabad for all the experimental support. The authors also wish to thank characterisation team at SSPL, Delhi for FE-SEM characterisation.

## CONTRIBUTORS

**Mr Amit** received his MSc (Physics) from Maharshi Dayanand University, Rohtak, India, in 2007. Presently working as a Scientist at DRDO-Solid State Physics Laboratory, Delhi. His current research interests include : Fabrication of AlGaN/GaN MMICs, modelling and simulation of HEMT devices.

In the present work he is instrumental in designing, implementing field plate structure in GaN HEMT fabrication process through ATLAS simulation and subsequently performance evaluation through electrical characterisation.

**Dr D.S. Rawal** received his MSc (Physics) and MTech (ECE) from University of Roorkee, Roorkee, in 1988 and 1990, respectively. He obtained his PhD in Experimental Plasma Physics from IIT Delhi, Delhi, in 2012. Presently working as a Scientist 'G' and heading GaN device fabrication team at DRDO-Solid State Physics Laboratory, Delhi. He has published more than 55 research papers in various international journals and conferences. His area of research includes: Development of GaN HEMT based MMIC Technology for microwave power applications.

In the current work he is involved in complete GaN HEMT process sequence formulation, process integration to fabricate multi-finger field plate HEMT device and its characterisation for validation.

**Mr Sunil Sharma** received his MSc (Physics) from Meerut University, Meerut and by MTech (Solid State Technology) from IIT Kharagpur, Kharagpur, India, in 2003. Presently working as a Scientist 'D' at DRDO-Solid State Physics Laboratory, Delhi. His area of research include: Development of GaN HEMT based MMIC process technology.

In the present work he is involved in PECVD SiN passivation and dry etching processes for device fabrication. **Dr Sonalee Kapoor** received her MSc (Physics) from St. Stephen's College, Delhi University, in 2000 and PhD in Physics from IIT Delhi, Delhi, India, in 2004. Presently working as a Scientist 'E' at DRDO-Solid State Physics Laboratory, Delhi. She has published more than 20 research papers in various international journals and conferences. Her area of research include: Development of GaN HEMT based MMIC technology and mainly working towards development of reliable ohmic/schottky contacts on AlGaN/GaN for HEMT microwave applications.

In the current work she has been involved in Ohmic, Schottky and field plate metallisation processes to fabricate multi-finger field plate GaN HEMT.

**Mr Robert Laishram** received his MSc (Physics) from University of Madras, Chennai, in 2000. Presently working as a Scientist 'E' at DRDO-Solid State Physics Laboratory, Delhi. He has published more than 05 research papers in international journal and conferences. His area of research include: Development of GaN based HEMT process technology and device characterisation. In the current work he is involved in Ohmic, Schottky and field plate metallisation processes and characterisation during multi-finger field plate GaN HEMT fabrication.

**Dr Rupesh Kumar Chaubey**, received his MSc (Physics) and PhD from BHU, Varanasi, India in 2001 and 2017, respectively. Presently working as a Scientist 'E' at DRDO-Solid State Physics Laboratory, Delhi. His area of research include: Development of GaN based high power devices for microwave applications. In the current work he has been involved in photolithography process and characterisation to fabricate multi-finger field plate GaN HEMT devices.

**Dr Seema Vinayak** received her MTech (Solid State Materials) and PhD (Physics) from IIT Delhi, Delhi, India in 1991 and 2007, respectively. Presently working as a Scientist 'G' and heading the GaN MMIC Division at DRDO-Solid State Physics Laboratory, Delhi. She has published more than 50 research papers in international journals and conferences. Her area of research include: Development of GaN HEMT based MMIC technology for microwave applications.

In the current work she has been mainly responsible for overall GaN HEMT fabrication process technology development and device characterisation.

**Dr R.K. Sharma,** obtained his MSc (Physics) and PhD from Department of Physics, BHU, Varanasi, India in 1978 and 1996, respectively. Presently working as a Distinguished Scientist and Director, DRDO-Solid State Physics Laboratory, Delhi. He has published more than 60 research papers in international journals. He is currently leading several R&D programs on development of strategic semiconductor materials and devices. His areas of interest include: Growth and characterisation of compound semiconductor crystals and epitaxial hetero-structures.

In the current study he has provided overall necessary guidance and support to carry out this work successfully.